Mitigating Supply Chain Obsolescence: Silicon, Fabrication Processes, and Wafer

Ensuring long-term component support for existing designs with wafer storage

Ensuring long-term component support for existing designs with wafer storage

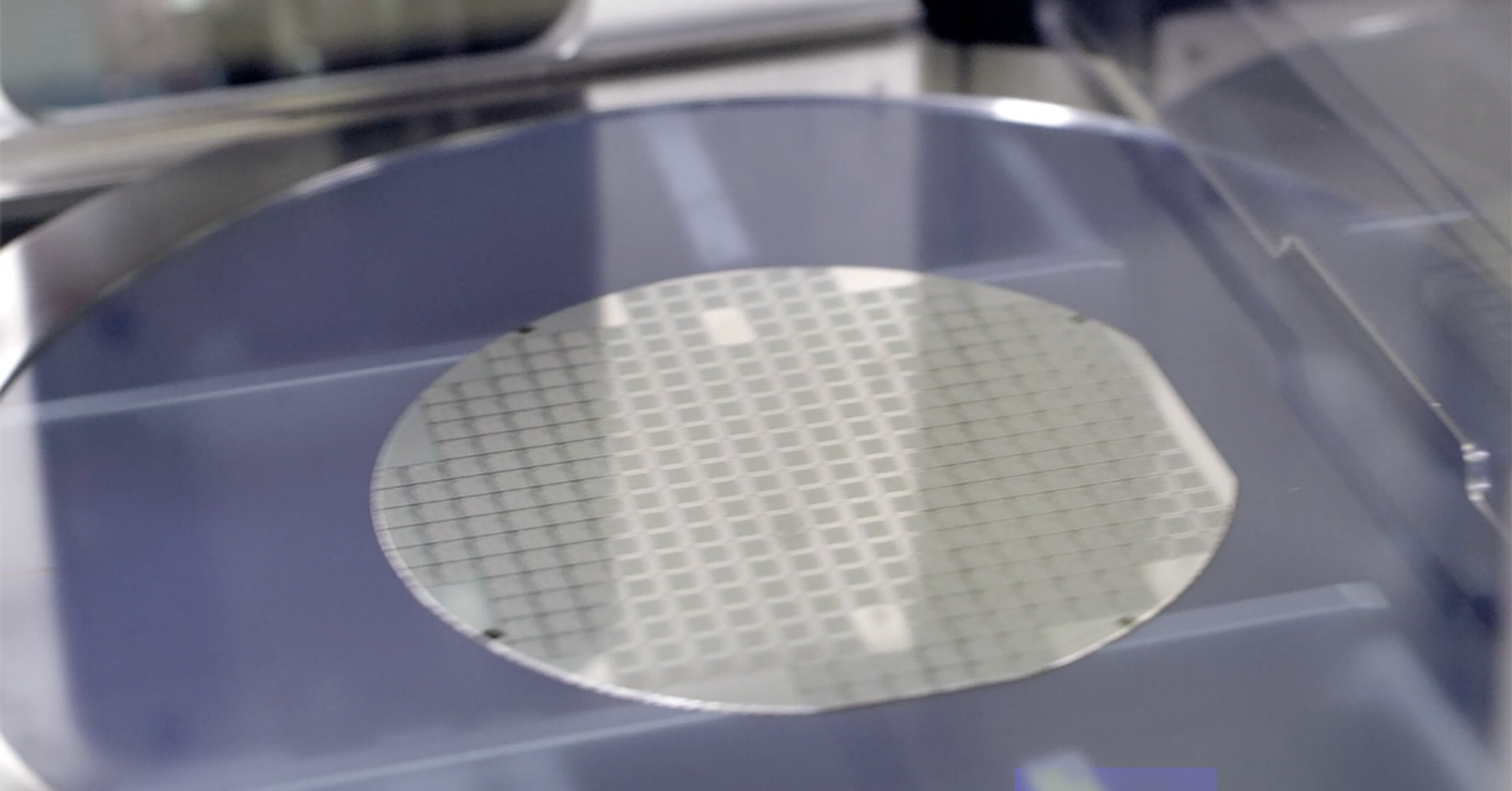

In part one of our exploration of the manufacturing puzzle, we reviewed the history of how and why semiconductor assemblies have moved away from classic lead frame assembly. To recap, these require expensive trim and form tooling, and the market has moved toward substrate Ball Grid Arrays (BGA), Quad Flat No-lead Packages (QFN), and Dual Flat No-lead Packages (DFN) type assemblies. In part two, we discussed how QFN and DFN assemblies, which are on the lower end of complexity and cost, will have a high impact on the future of SOIC and low pin-count PLCC assemblies. Now, in part three, we direct our focus toward wafer storage and semiconductor fabrication technologies.

What drives demand for wafer storage and is it always there?

As with many technological challenges, the answer is complicated and to understand the answer’s subtilties we must go into details.

The argument for wafer storage is rather simple and composed of two ideas. Firstly, assembly and test costs are avoided when the fabrication process is discontinued. Secondly, wafers can be stored in less space and for a longer time than assembled products. Both points are true, especially regarding older products, but only as long as:

- Assembly and test can still be accomplished.

- The wafer product state is fully tested and or configured.

The first condition may look obvious, but many overlook the potential meaning. The assembly or packaging needs to remain available for wafer storage to continue making sense. The test platform must persist in viability for as long as wafer storage is required. In our previous manufacturing puzzle articles, we discussed packaging and how classic lead frame technologies are on the way out. Tester platforms and appropriate external circuitry must be available for the entire desired duration of wafer storage. If tester availability cannot be assured, test program porting is another cost considered for the financial viability of wafer storage. This first condition can be overcome with proper planning and preparation. Rochester Electronics has been investing in assembly and test to continue to make wafer storage viable.

The second part of the argument regarding the need for wafer products to be fully tested and or configured is far more complicated. For the past half-century of wafer storage in the semiconductor industry, it has been straightforward to understand product complexity and that test and assembly assured viability. Today this is far less simple. Several factors are driving wafer product state complexity, including:

- Commodity memory products do not exist in isolation. Since advanced node mask costs are so high, it is becoming common for a single mask set to represent several wafer sort fuse operation-selected products. It is not unusual for the same wafer to represent 4-to-8 different final products.

- Knowing the inventory position of any of the products individually is unclear with multi-product wafers.

- EEPROM memory usually requires a high-temp wafer sort operation before assembly. This implies that a wafer sort test program must be part of the wafer storage process.

- Products with large onboard memory are forced to implement Built-In Self-Repair (BISR) to yield a wafer sort operation. This is true for most technologies at 65nm and below, where the die area is primarily memory. BISR is run as a wafer sort operation, usually followed by fusing to enable redundant memory columns or rows to be swapped in and improve yield. BISR algorithms are proprietary and unique to every semiconductor company or IP provider.

- Wafer product that is Flip Chip needs to be bumped to be assembled. Bumping metallurgy matters and it’s not yet clear if bumps with any lead content have long-term reliability concerns. More studies need to be done. Wafer storage could be done without bumping, but then the operations of BISR and fusing would need to be enabled over time.

- If a wafer product is in a BGA assembly, there will need to be a substrate available for the die to be bonded to or flip-chip assembled. Substrates do not have long shelf lives and must be procured in order quantities that usually exceed long-term system demand. Long-term substrate storage is something that also needs further studies.

Answering what drives wafer storage and whether is it always there, the real answer is that it depends on the product. All conditions examined above need to be understood for the final assessment of viability.

When are wafers available at a Last Time Buy (LTB) event?

The reality is that wafer storage availability is not often an option presented to end customers. The financial expectations of an LTB are for finished goods, and a short-term bump in revenue as a result before the LTB event closes. There is inherent resistance to settling for less revenue than finished goods for LTB events. The event will already be forecasted, and the revenue already planned for. This should be part of the business plan before it happens. Fabless semiconductor companies have an external supply chain for most products. Semiconductor fabrication, assembly, and testing are mostly subcontracted items. They do not typically have an exit point in their product manufacturing flow for only wafers. In short, most fabless semiconductor companies have not identified wafers alone, as a development item or deliverable.

Discussions about wafer storage with a fabless semiconductor company should occur before the LTB event, or the odds of having proper storage are dramatically reduced. The Integrated Device Manufacturers (IDM) who own their fabrication facilities may do things differently. IDMs have more control over every step in their product development flow. IDMs are more likely to have a wafer buy than fabless companies, but this discussion must happen before an LTB event, or the chance may be lost.

Wafer availability at an LTB event is complicated and rare. The odds of procurement after an LTB event has been announced is low. Proper planning from product management teams and companies like Rochester Electronics increases the odds of successfully implementing a long-term wafer storage agreement. Rochester Electronics has billions of die under storage and continues to grow our product selection to provide long-term system customers with the fully authorized products needed for decades of system life. Furthermore, Rochester has determined that product can be stored for decades, ensuring supply for customers.

As a licensed semiconductor manufacturer, Rochester has manufactured over 20,000 device types. With over 12 billion die in stock, Rochester has the capability to manufacture over 70,000 device types.

For over 40 years, in partnership with over 70 leading semiconductor manufacturers, Rochester has provided our valued customers with a continuous source of critical semiconductors.

Rochester Electronics offers a range of services at our Newburyport facility to extend semiconductor product lifecycles with wafer storage and die processing services.

Wafer Processing

- Wafer back-side grind

- Wafer dicing

- Die pick and place

- Die inspection

Die Banking

Long-Term Storage

- Long-term storage and managed logistics manufacturing programs

- Lot acceptance and reliability test services to ensure full product functionality

- Parts management

- Usage reporting

- Associated documents are converted and stored electronically

- ERP control of wafer inventory and attributes

- Electronic Wafer map generation for inked wafers

Next-Generation Storage

- ISO-7/10K certified

- Enhanced ESD controls

- ISO-5 Inspection areas

- Relative humidity control

- Real-time monitoring of temperature and humidity

- Auto-purge on power fail

- Secure room and individual cabinets

Do you want to learn more? Contact us today.

Read Part 1: Mitigating Supply Chain Obsolescence: Exploring the Semiconductor Manufacturing Puzzle

Learn more about Rochester’s wafer processing and storage solutions

WATCH: to explore our wafer processing and storage capabilities